|                                    |                         |              | PPd |

|------------------------------------|-------------------------|--------------|-----|

|                                    |                         |              |     |

|                                    |                         |              |     |

| Heavy Flavo                        | our Identification      | on at the IL | C   |

|                                    | nental Particle Physics | Seminar      |     |

| CPP-1 Settings                     | University of Edinburg  | gh vine      |     |

|                                    | RCLK Fragmeney (MP4z)   |              |     |

|                                    | Joel Goldstein          |              |     |

| FPGA 1 Test Output 1 Test Output 2 | Rutherford Appleton L   | aboratory    |     |

|                                    |                         |              |     |

- **1. Introduction to the ILC and Heavy Flavour ID**

- 2. LCFI Research Programme:

- I. Simulation and Physics

- **II. Mechanical Development**

- **III. Sensor Development**

- 3. Summary

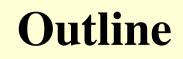

### L C F I The International Linear Collider

#### 500-1000 GeV e<sup>+</sup>e<sup>-</sup> collider

- Superconducting RF

- Start in ~2015

- Complimentary to LHC:

- Precision measurements

- Searches

Many physics channels require excellent *heavy flavour ID Higgs, SUSY, Top....*

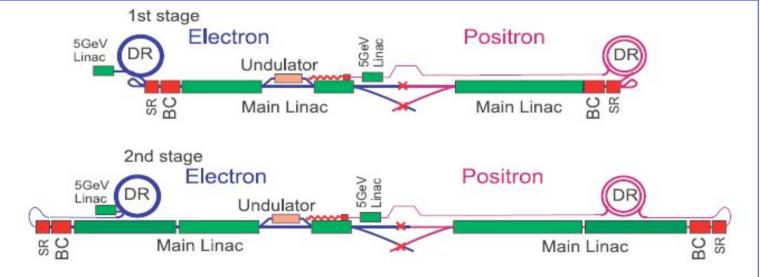

# **Heavy Flavour Identification**

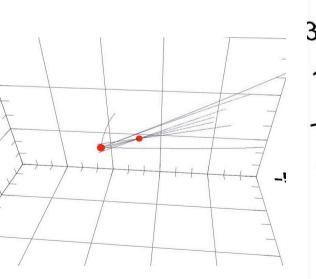

Heavy flavour particles with lifetime ~1 ps  $(\tau, b \text{ and } c)$ travel a few mm then decay.

#### Precision silicon detectors can reconstruct decay vertices.

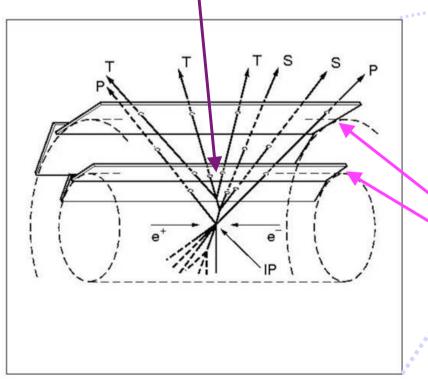

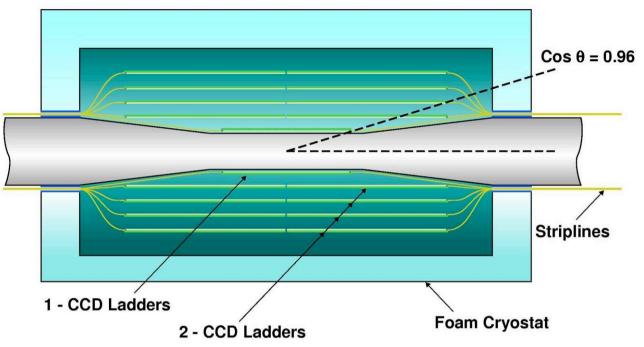

## **Baseline Vertex Detector**

- 800 Mchannels of 20×20 μm pixels in 5 layers

- **Optimisation:**

- Inner radius (1.5 cm?)

- Readout time (50 μs?)

- Layer thickness  $(0.1\% X_0?)$

PP

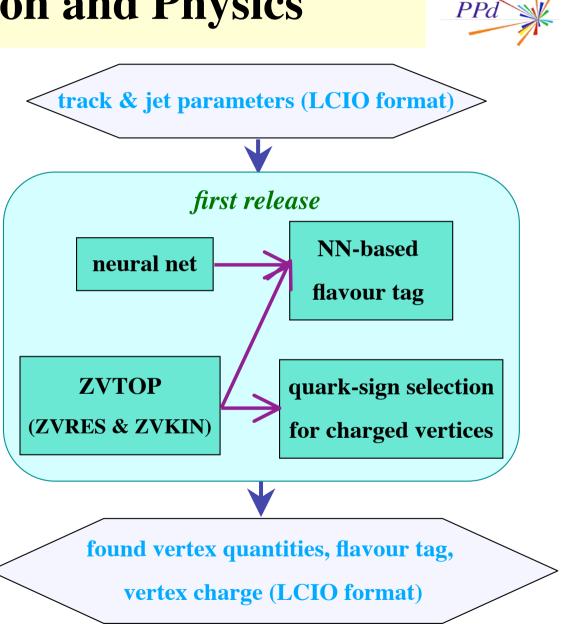

# **Simulation and Physics**

- 1. Optimise detector design

- Need reliable tracking

- Been using Fortran/SGV

- 2. Develop vertex tools

- Work within common framework

- Writing C++ package

- 3. Physics analysis

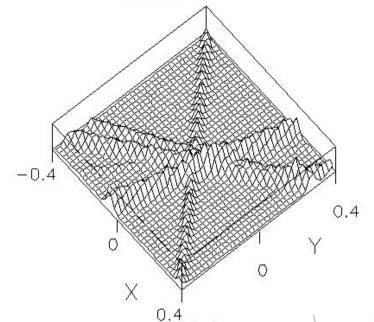

## ZVTOP

- Topological vertex finder

- Developed at SLD

- Being ported to C++ (JAVA at SLAC)

- Used as basis for flavour tag

## **Vertex Charge**

Do more than identify *b*, *c* quarks...

- 1. Find vertices with ZVTOP

- 2. Attach candidate tracks

- 3. Measure charge

#### Can tell quark from antiquark!

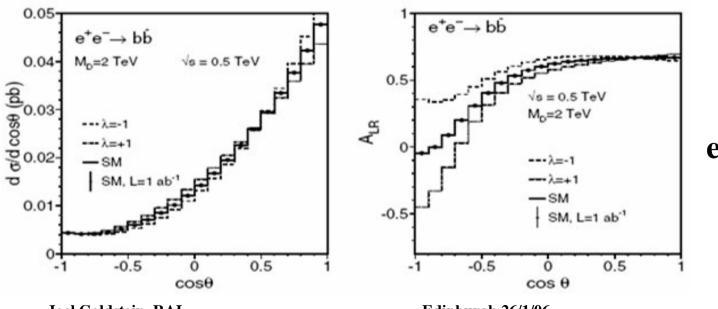

#### e.g. LED scenarios

# **Vertex Charge in Physics**

LCFI

PPe

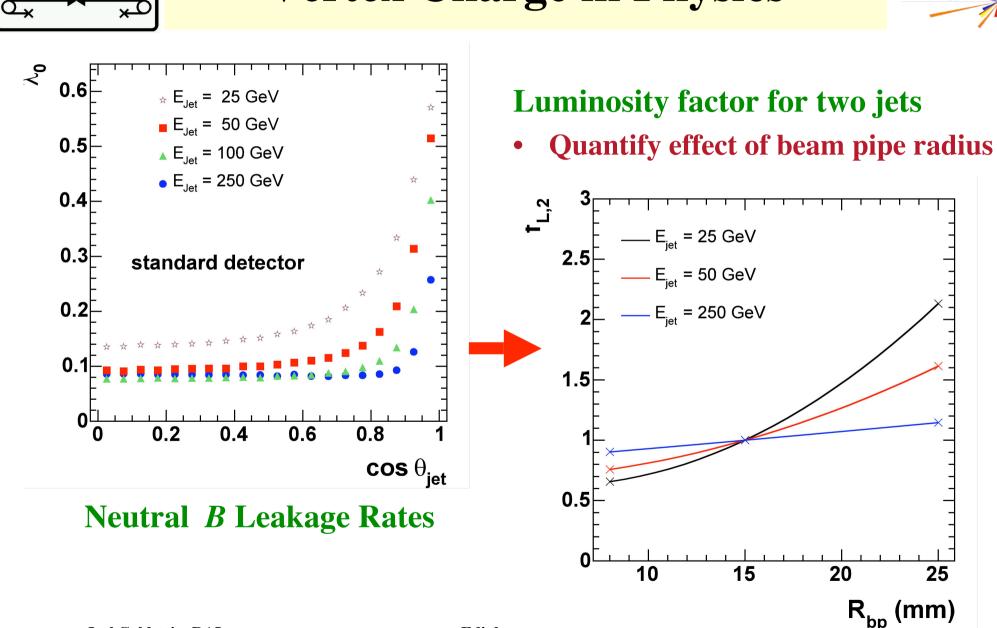

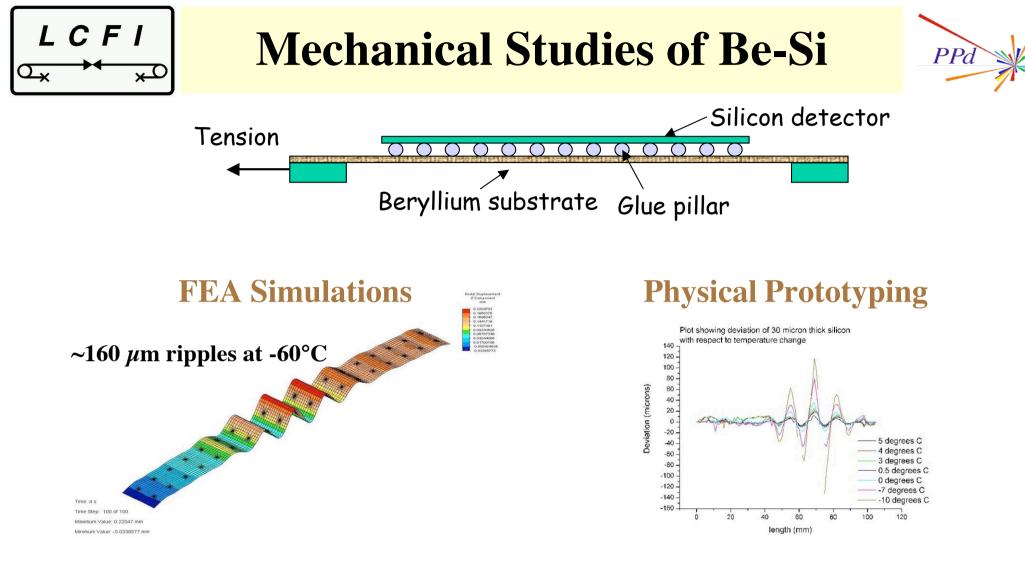

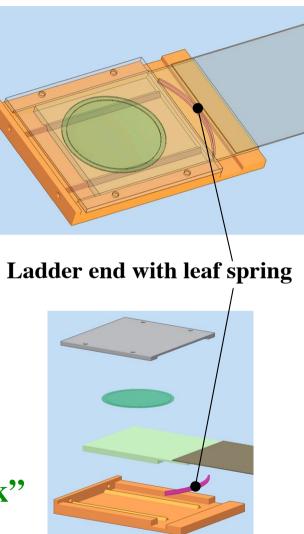

## **1. Thin Ladder Mechanics**

- Materials and designs for  $\Delta T \approx 100 \text{K}$

- Preference for uniform material in tracking volume

- CCDs routinely thinned to epitaxial layer

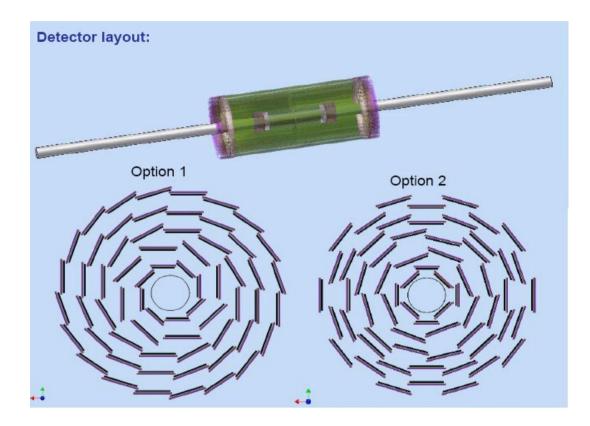

# 2. Global Design

Ensure ladder designs practical

# **3.** Cooling

• Gas cooling has always been assumed...

# **Mechanical Options**

Target of 0.1% X<sub>0</sub> per layer(100µm silicon equivalent)

- 1. Unsupported Silicon

- Longitudinal tensioning provides stiffness

- No lateral stability

- Not believed to be promising

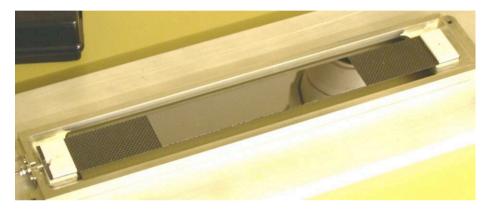

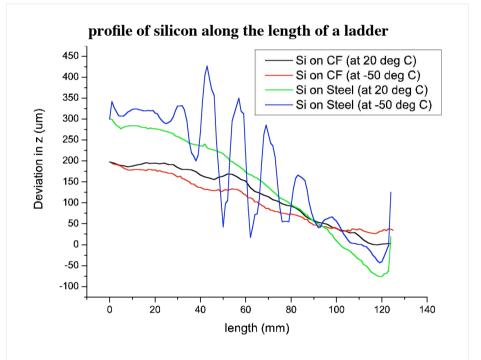

#### 2. Thin Substrates

- Detector thinned to epitaxial layer (20μm)

- Silicon glued to low mass substrate for lateral stability

- Longitudinal stiffness still from tension

- Beryllium has best specific stiffness

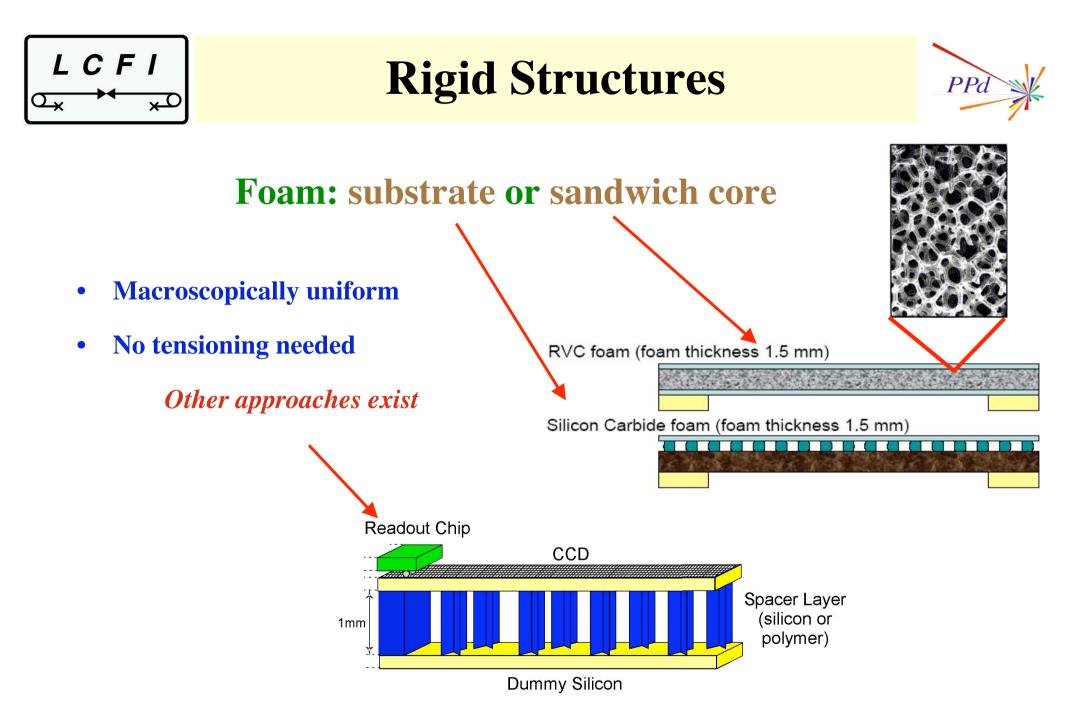

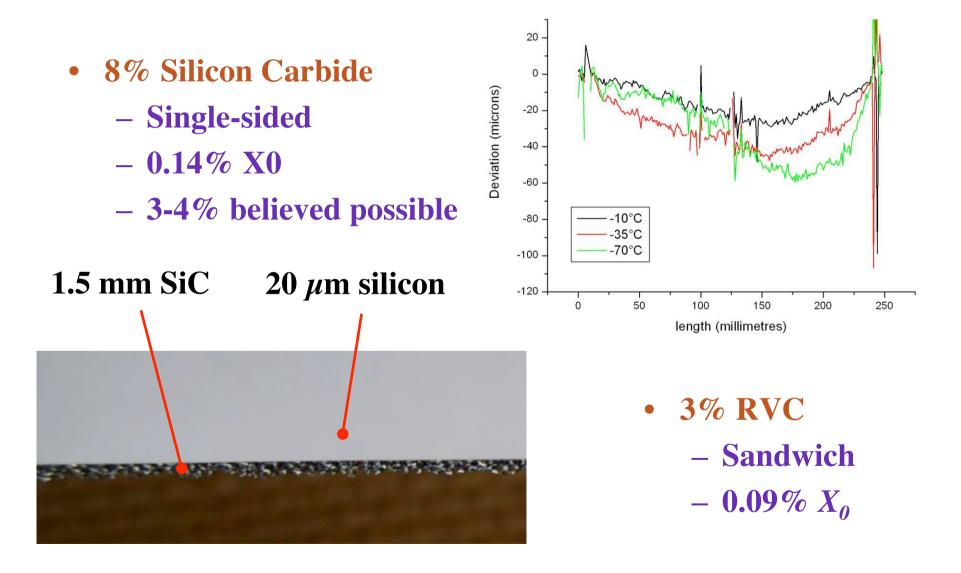

#### 3. Rigid Structures

#### Good qualitative agreement

• Minimum thickness ~  $0.15\% X_0$

## **Carbon Fibre Substrates**

#### • Carbon fibre has better CTE match than beryllium

- Prototype ~ 0.09% X<sub>0</sub>

- No rippling down to < 200K</p>

- Lateral stability insufficient

• Other thin substrates under consideration

## **Foam Prototypes**

# **Cooling Studies**

Gas cooling test stand Temperature (Streamline 1) 2.930e-002 - Cold nitrogen flow - Model of 1/4 detector 2.680e-002 - 2.430e-902 6 20 litres / min 17.5 litres / min 15 litres / min 2.180e+002 12.5 litres / min \* 10 litres / min 4  $P_g / W$ 7.5 litres / min 5 litres / min 1.930e+002 [K] 2 0.055 0.062 (m) .027 **Parallel CFD simulation work** -5 5 15 20 10 25 T<sub>surface</sub>-T<sub>gas</sub> / K -2

## **Global Design Work**

#### • Enough detail for ladder design "sanity check"

Joel Goldstein, RAL

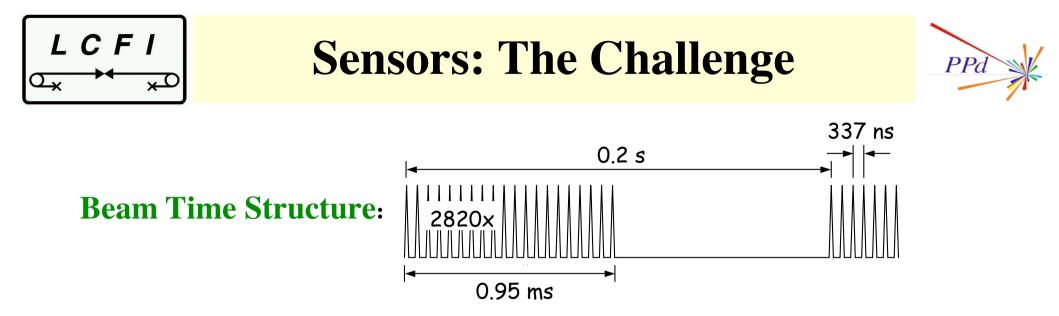

#### What readout speed is needed?

- Inner layer 1.6 MPixel sensors

- Once per bunch = 300ns per frame : *too fast*

- Once per train ~200 hits/mm<sup>2</sup> : *too slow*

- 10 hits/mm<sup>2</sup> => 50µs per frame: just right (Fastest commercial imaging ~ 1 ms/MPixel)

#### **Power dissipation – gas volume cooling**

## **Sensor Research**

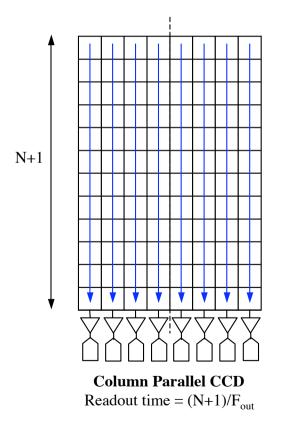

#### 1. Column Parallel CCDs

- Focus so far building on past experience

- Readout during bunch train

- Clock drive major challenge

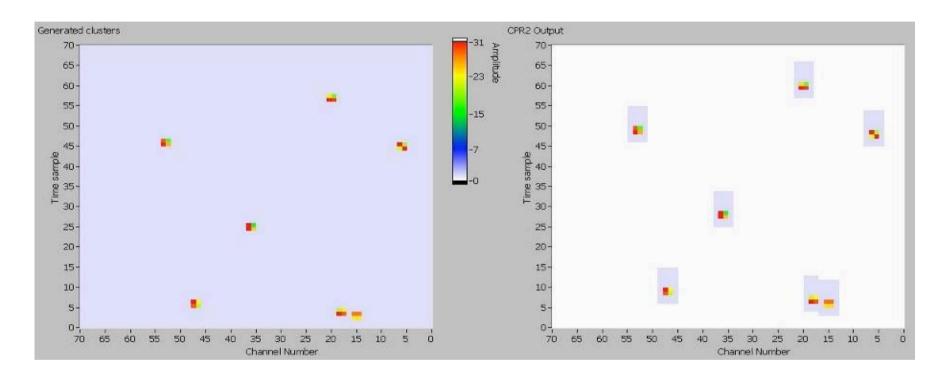

- 2. Image Sensor with In-situ Storage

- Increased robustness

- Reduced driver requirements

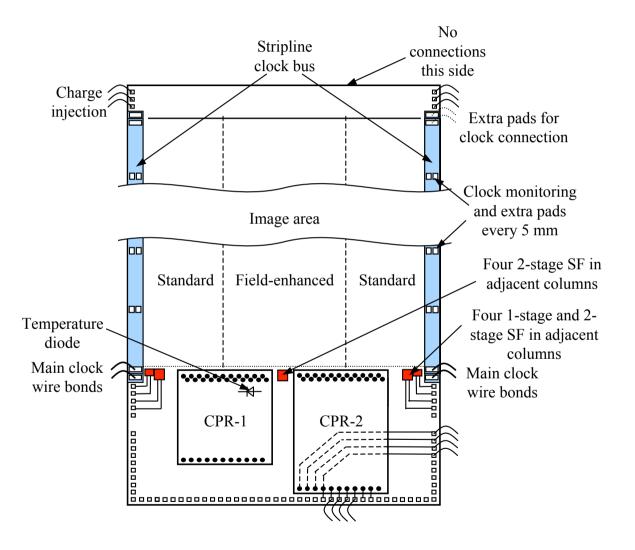

# **Column Parallel CCD**

- Separate amplifier and readout for each column

- 50 MHz clock rate

• Clock drive is real challenge

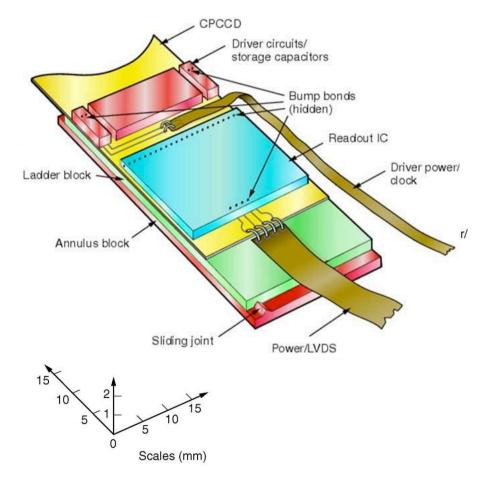

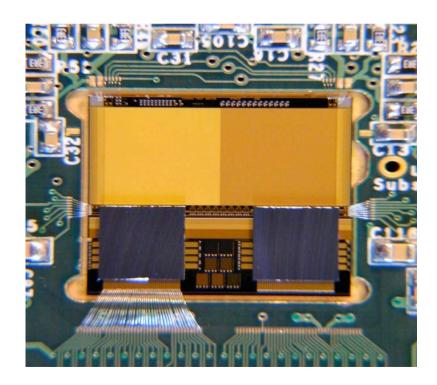

### **Prototype CP CCD**

### **CPC-1** produced by e2v

- Two phase operation

- **Metal strapping for clock**

- 2 different gate shapes

- **3 different types of output**

- 2 different implant levels

#### Clock with highest frequency at lowest voltage

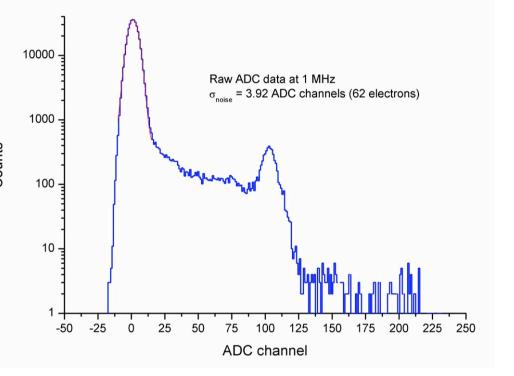

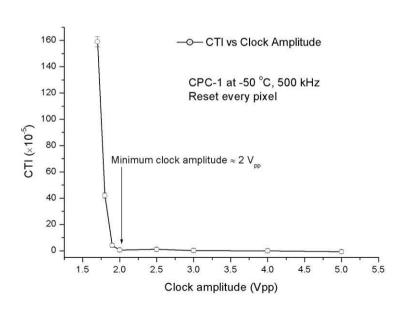

## **CPC-1 Results**

- Noise ~ 100 electrons (60 after filter)

- Minimum clock ~1.9 V

Maximum frequency > 25 MHz

inherent clock asymmetry

Joel Goldstein, RAL

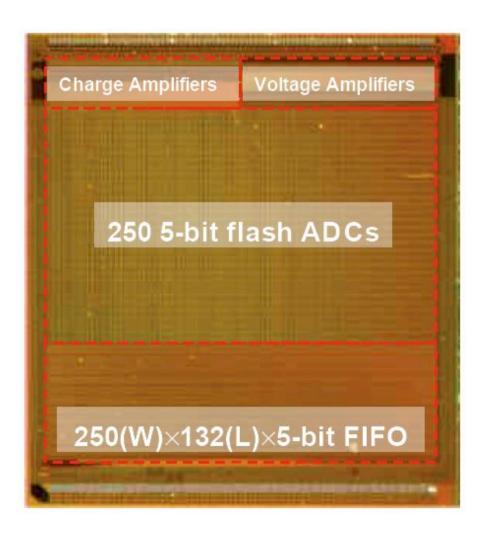

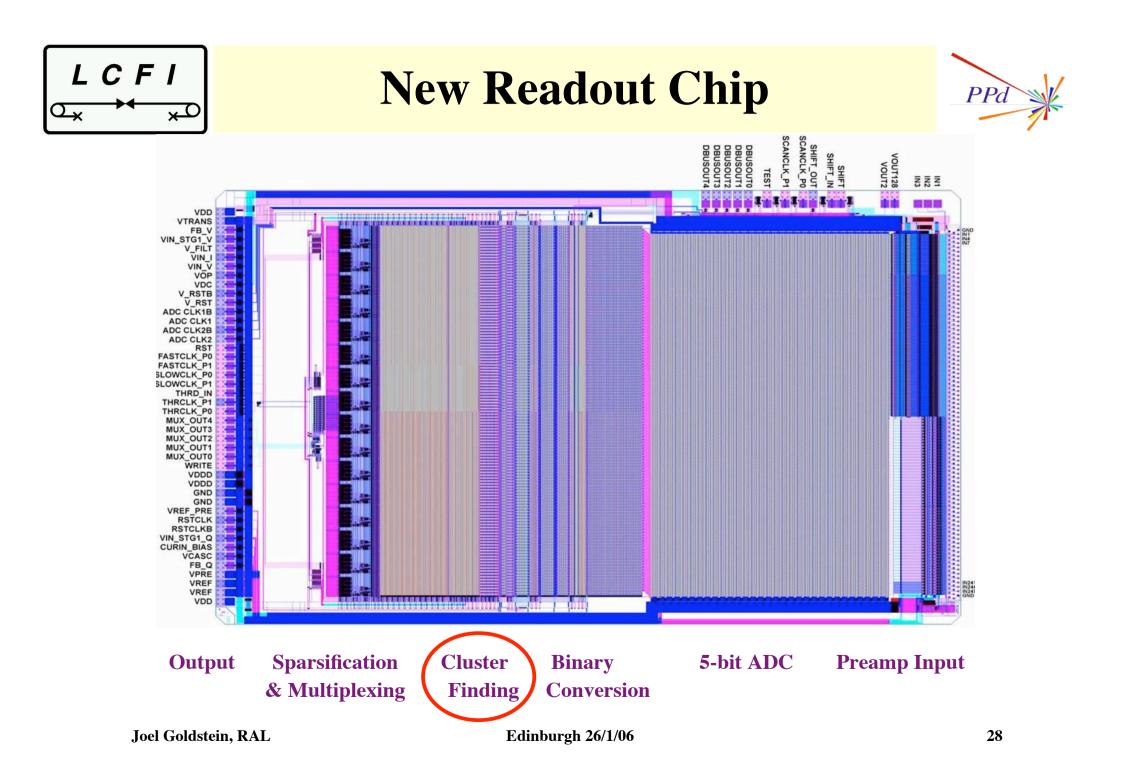

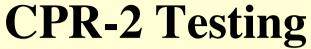

# **CP Readout ASIC**

### **CPR-1 designed in house**

- IBM 0.25 µm process

- Bump bonded to CPC

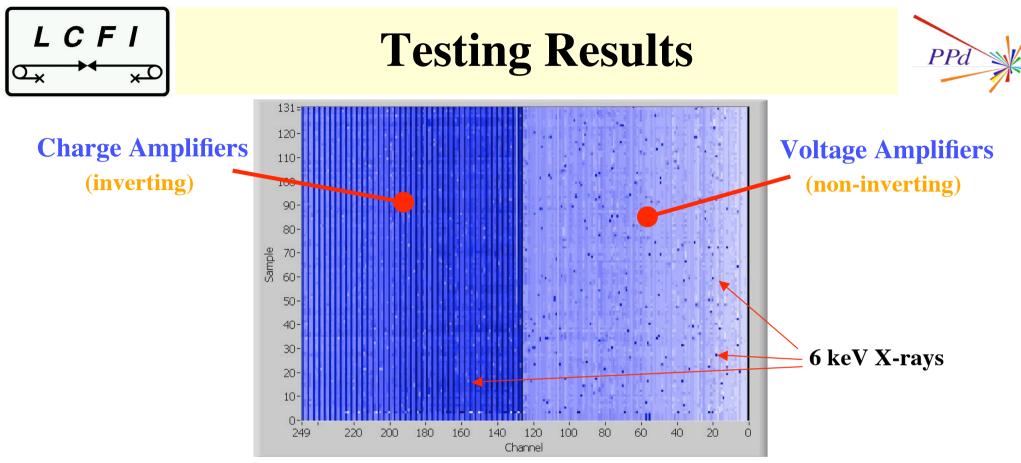

- Charge amplifiers work

- Negligible noise from CPR

- Column parallel operation demonstrated

- No signal in ~20% of voltage channels

- Readout chip very sensitive to timing and bias issues

- Gain decrease towards centre of chip

# **The Second Generation**

- CCDs

- Larger and faster prototypes

- Clock drivers

- Radiation effects

- ASICs

- More robust

- Cluster finding logic

- Hostile RF environment:

- Large EM leakage from ILC bunch train

- Charge-voltage conversion dangerous

- Store multiple charge samples locally

- Readout all samples during 200ms dead time

- Double metal now available from e2v

- Symmetric clock design

- "Busline-free" option

- Distributed clock planes

- Faster

- More uniform

- Compatible with old and new readout chips

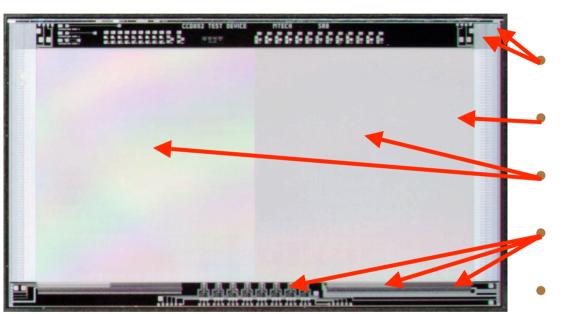

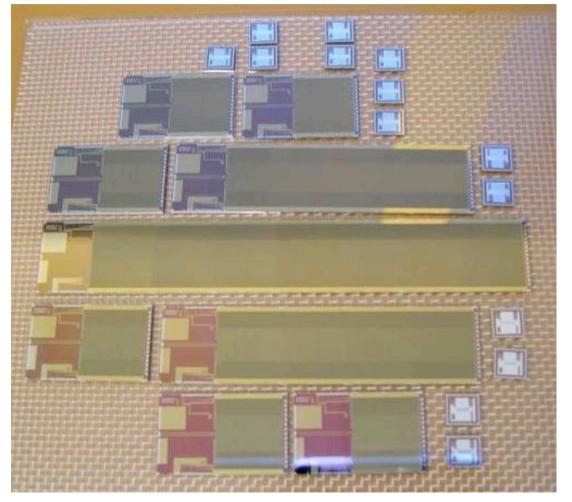

### **CPC-2** Production

- Dedicated batch at e2v

- 3 sizes of CPCCD

- up to 92 mm active length

- First devices delivered

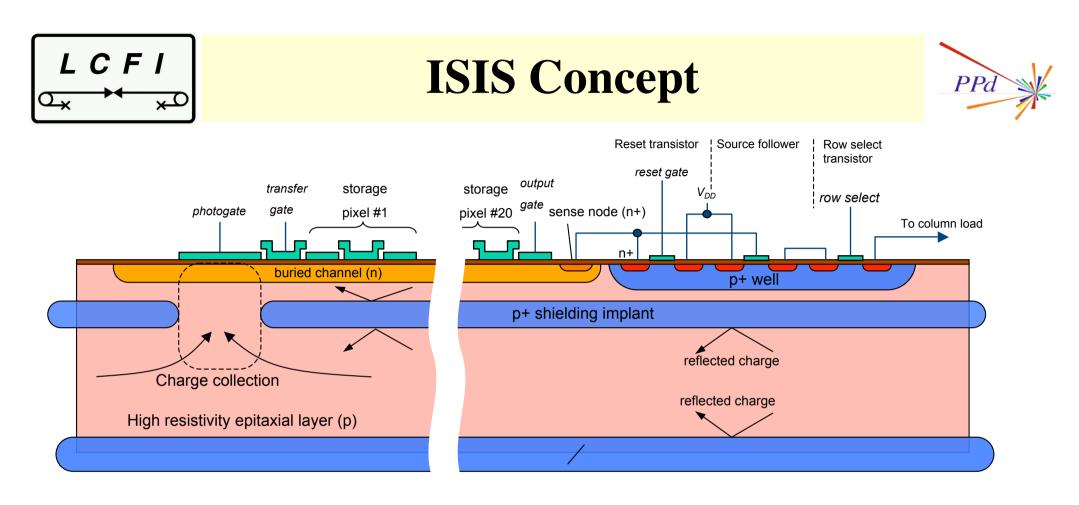

- Wafers include 16×16 ISIS

- Cluster finding logic and sparse readout

- Improved amplifiers and ADCs

- Increased robustness

- Orders of magnitude increased resistance to RF

- Much reduced clocking requirements (*readout ~1MHz*)

- Combination of CCD and CMOS technology on small pitch *Ideal burst imager is it practical for the ILC?*

**5 cell CCD Register**

Photogate 8×8µm<sup>2</sup>

- Proof-of-principle

- 16×16 array

- e2v design rules

#### **Output and reset transistors**

LED flash in 3<sup>rd</sup> cell

# Summary

- First generation sensors extensively studied

- Column parallel CCD principle proven

- Direct charge output demonstrated

- Starting to text next generation

- Detector-scale CCDs, sparsification

- ISIS principle proved

- 0.1%  $X_0$  ladders seem achievable

- Foams looking promising

- Qualitative detector optimisation

- Delivering tools to global ILC community

### **Exciting times ahead!**