## Front end electronics for the Advanced Implantation Detector Array (AIDA) detector in DESPEC at NUSTAR

Presented by Ian Lazarus

lan Lazarus NPG, CCLRC Daresbury

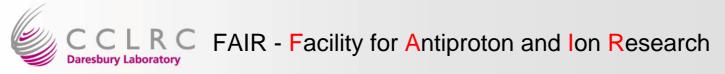

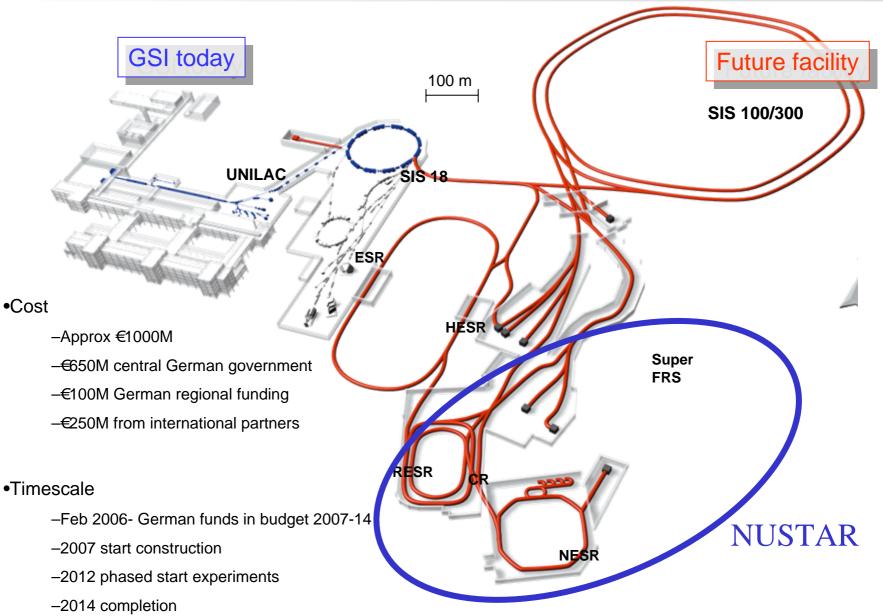

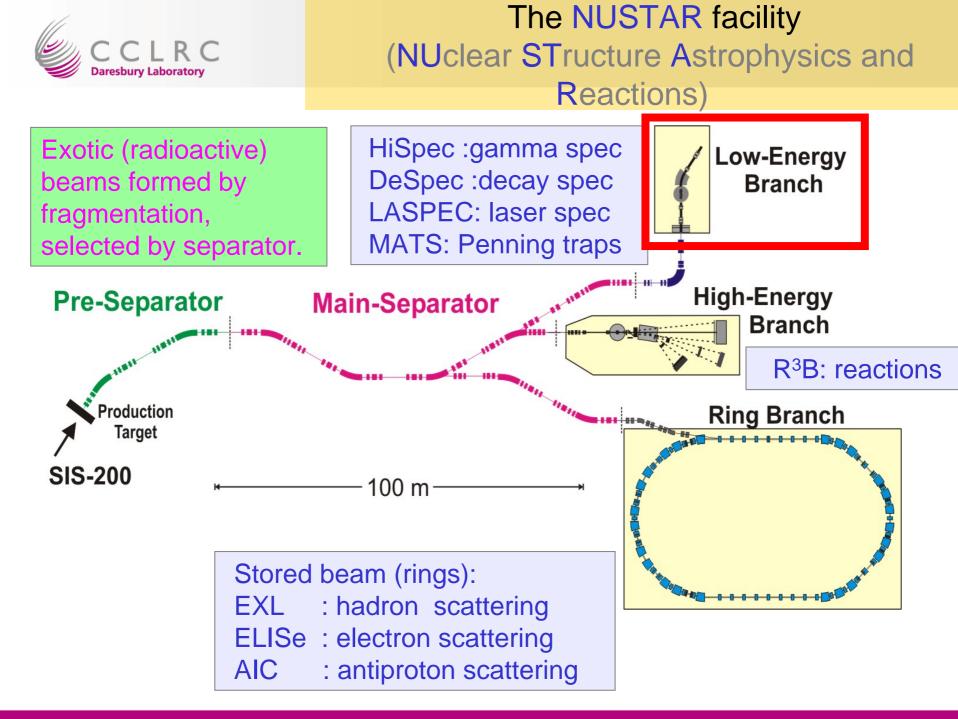

#### NUSTAR Low energy branch

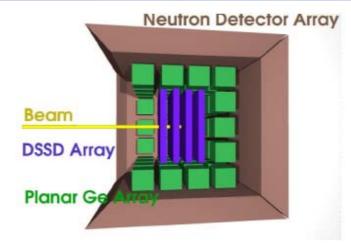

Fig. 1 Overview of the experimental area of the Low-Energy Branch

# AIDA for DESPEC- the concept

### **Advanced Implantation Detector Array (AIDA)**

- Super FRS Low Energy Branch (LEB)

- Exotic nuclei energies ~50-150MeV/u

- Implanted into multi-plane DSSD array

- Implant decay correlations

- Multi-GeV DSSD implantation events

- Observe subsequent p, 2p,  $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\beta$ p,  $\beta$ n ... decays

- Measure half lives, branching ratios, decay energies ...

- DSSD segmentation ensures average time between implants for given x,y quasi-pixel >> decay half life to be observed.

- Implies quasi-pixel dimensions ~ 0.5mm x 0.5mm

# AIDA for DESPEC- the detector

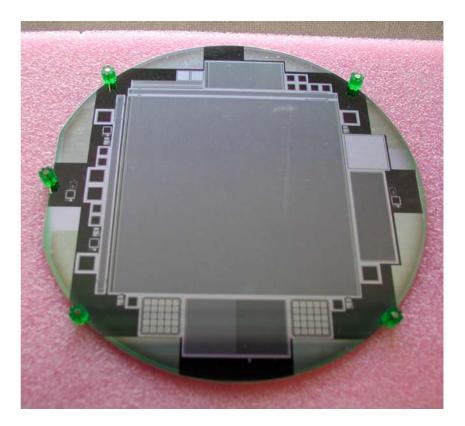

### DSSD

Technology well established (e.g. GLAST LAT tracker)

- 6" wafer technology

10cm x 10cm area

- 1mm wafer thickness

- Integrated components

a.c. coupling

polysilicon bias resistors

... important for ASICs

- Series strip bonding

8.95 cm square Hamamatsu-Photonics SSD before cutting from the 6-inch wafer. The thickness is 400 microns, and the strip pitch is 228 microns. Slide from Tom Davinson

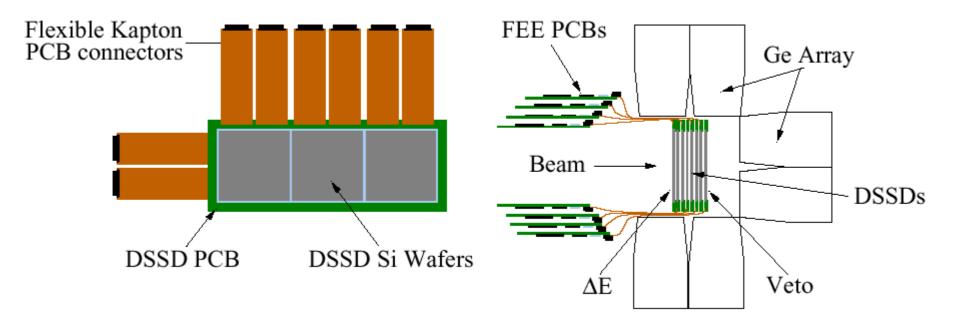

## AIDA for DESPEC

### **General Arrangement**

# AIDA for DESPEC- Instrumentation

### Instrumentation

#### Why use of Application Specific Integrated Circuit (ASIC) technology?

- •Large number of channels required (8 x (128+(3x128))= 4096)

- Limited available space

- •Cost

#### **Outline ASIC Specification**

- Selectable gain: low 20GeV FSR high 20MeV FSR

- Noise  $\sigma$  ~ 5keV rms.

- Selectable threshold: minimum ~ 25keV @ high gain ( assume  $5\sigma$  )

- Integral and differential non-linearity

- Autonomous overload recovery  $\sim \mu s$

- Signal processing time <10µs (decay-decay correlations)

- Receive timestamp data

- Timing trigger for coincidences with other detector systems

DSSD segmentation reduces input loading of preamplifier and enables excellent noise performance.

## • Problem

Multi GeV implant followed by decay in region of 1MeV e.g. 20GeV/1MeV = 2.10<sup>4</sup> dynamic range

## Some possible solutions

- Logarithmic preamps

- Makes analysis difficult

- High/low gain preamp pairs (with clamping)

- Doubles power, halves packing density

- Fast recovery from saturation

- Look at this one first

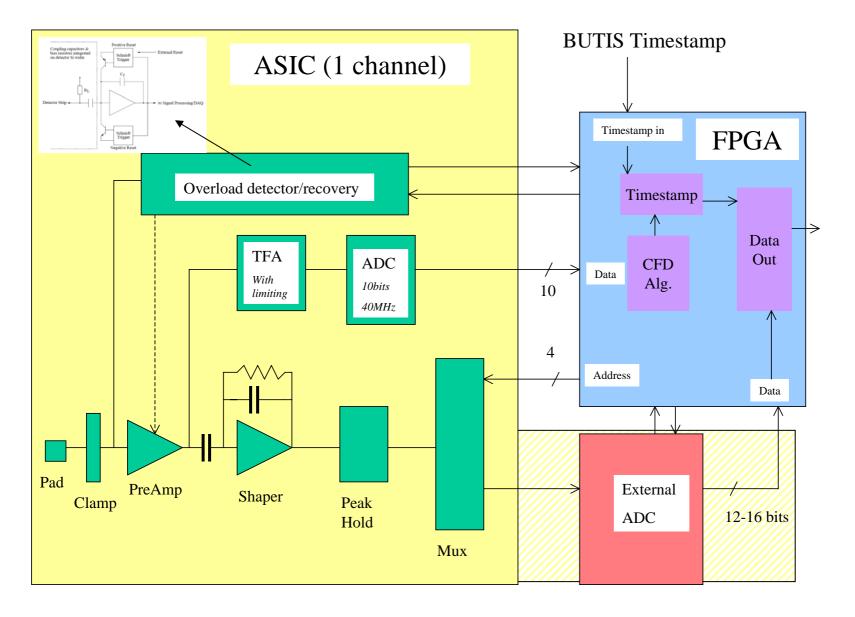

#### 1 of the 16 channels in the DESPEC Implantation Detector ASIC (shown with external FPGA and ADC)

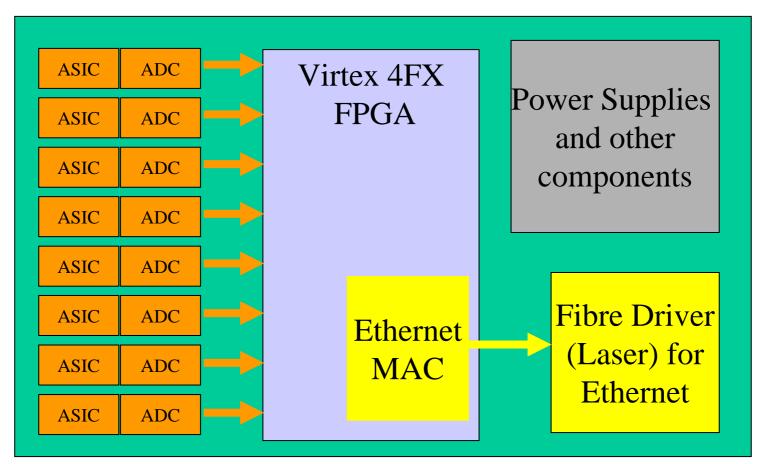

128 Channel FEE Card for DESPEC

### 16 ch ASIC (with ADC?)

128 detector signals in; 1 data fibre out

Estimated size: 80x220mm, Estimated power 25W per 128ch (800W total)

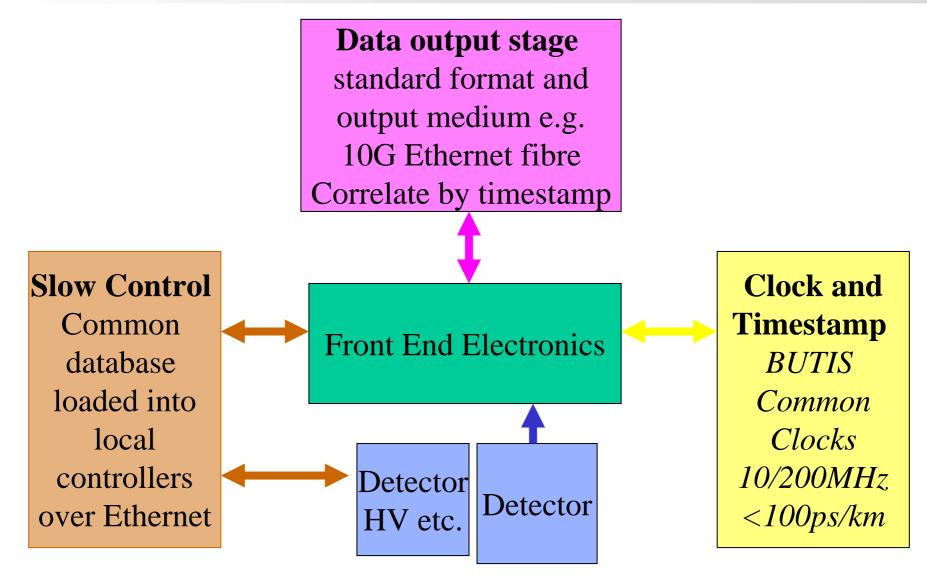

NUSTAR- Defining 3 common interfaces or docking stations

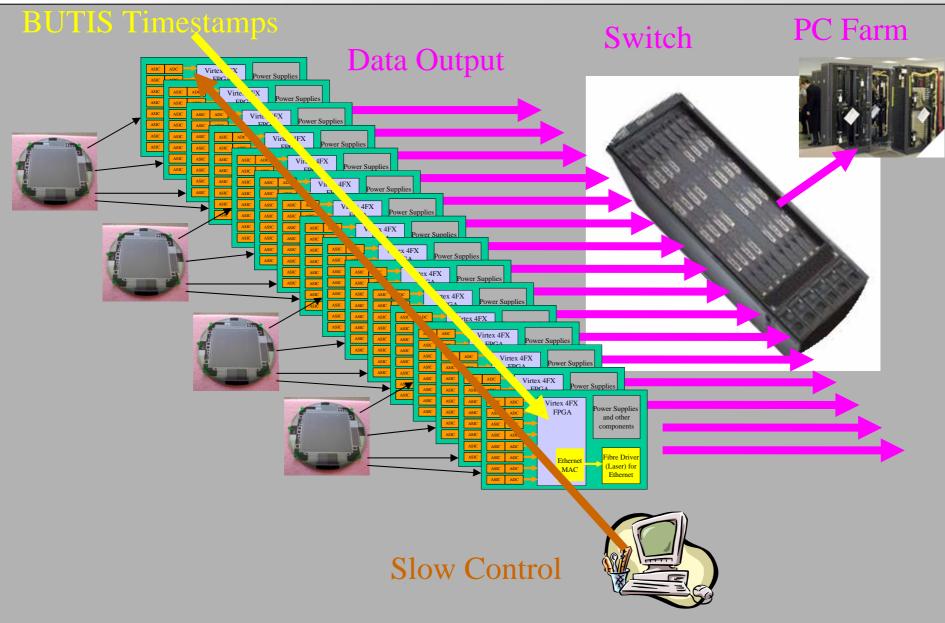

# Diagram of half of AIDA system

# The AIDA project- summary

- Objective:

- To construct a new generation ASIC-based Double-sided Silicon Strip Detector system for decay spectroscopy experiments of exotic nuclei on the new FAIR accelerator facility at GSI, Darmstadt, Germany.

- To commission and test this system in-beam, and perform ongoing implantation-decay experiments, primarily at GSI, prior to the availability of beams from FAIR.

- 4 years funding from 2006-2010 announced May 2006

- Collaboration:

- Detectors and project management- University of Edinburgh

- FEE, ASIC, DAQ CCLRC

- Postdoc (detector/physics) Mechanics- University of Liverpool

- Total 35 40 FTE allocated to this project (scientists, engineers, mechanical designers, technicians)