# AIDA detailed design

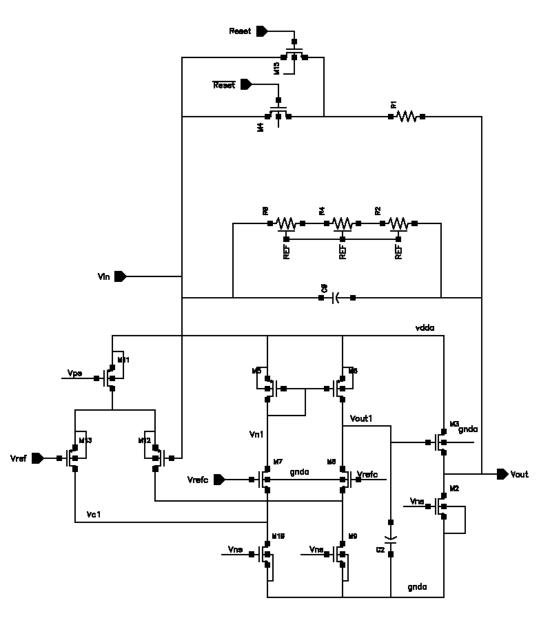

Amplifier feedback options

Steve Thomas ASIC Design Group

20th February 2007

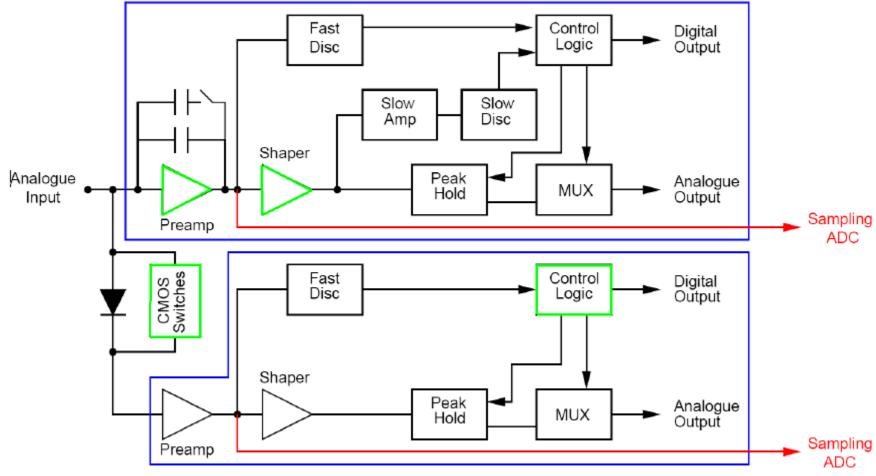

Low & Intermediate Energy Range

High Energy Range

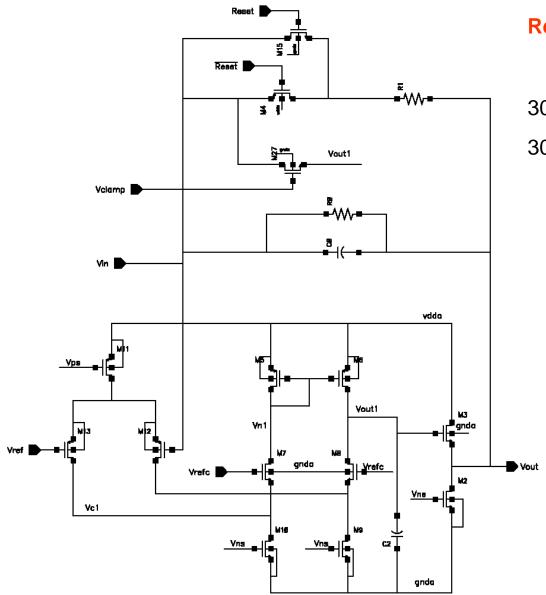

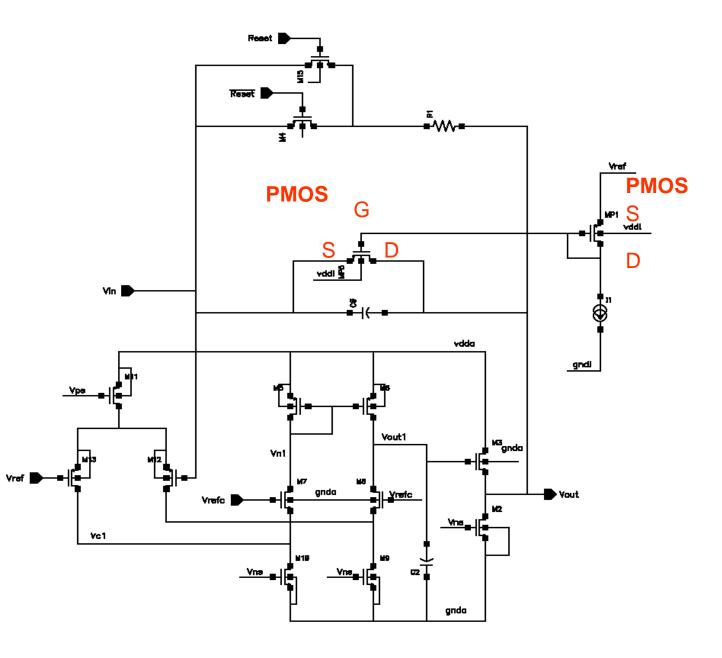

#### **Resistive feedback - idealised model**

$30M\Omega$ , no parasitic capacitance

$30\mu s$  time constant

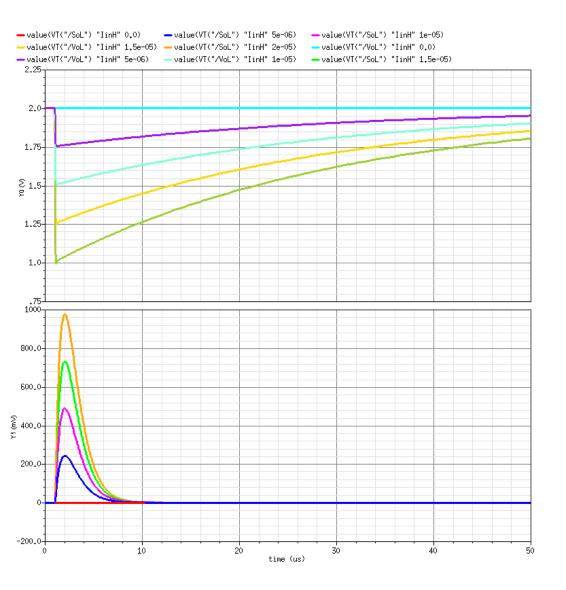

#### **30M resistor - no capacitance**

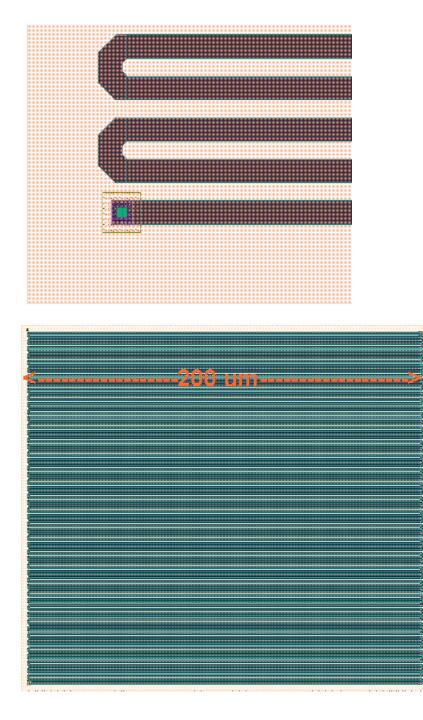

#### **Feedback resistor**

Poly2 : 1.2k $\Omega$  per square

~3pF parasitic to substrate

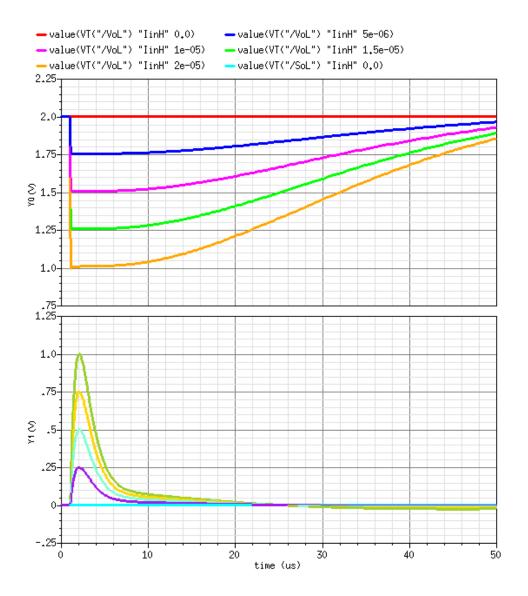

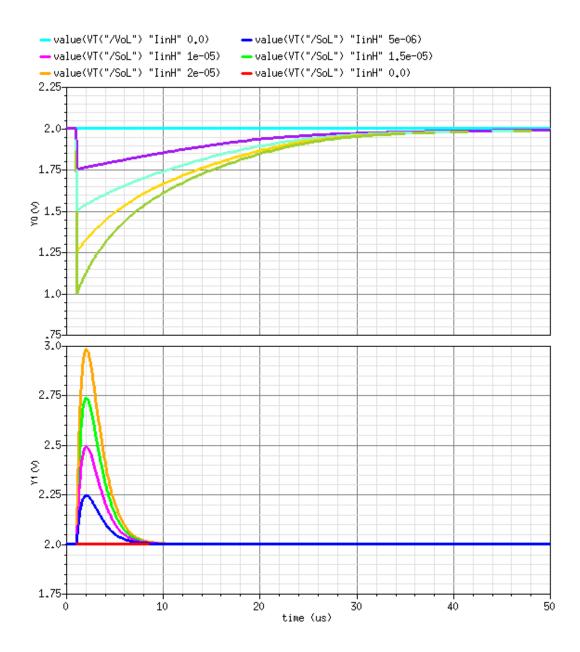

#### **Resistive feedback**

30M $\Omega$ , with capacitance ~1pF per 10M $\Omega$  segment

~10 $\mu$ s time constant

#### **30M resistor - with capacitance**

#### **30M resistor - with capacitance**

Pole-zero failure

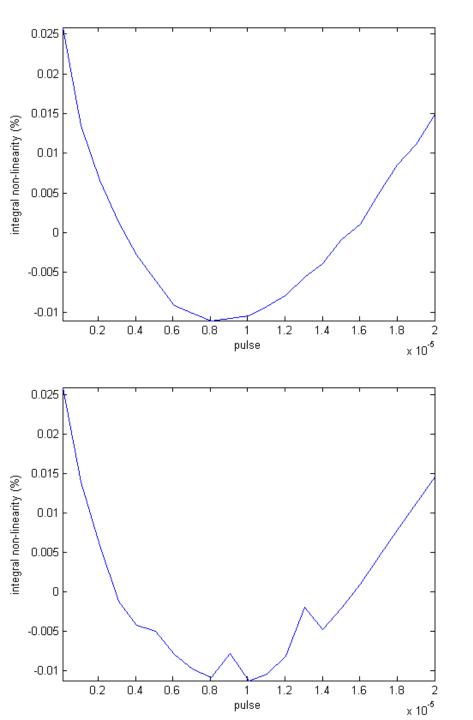

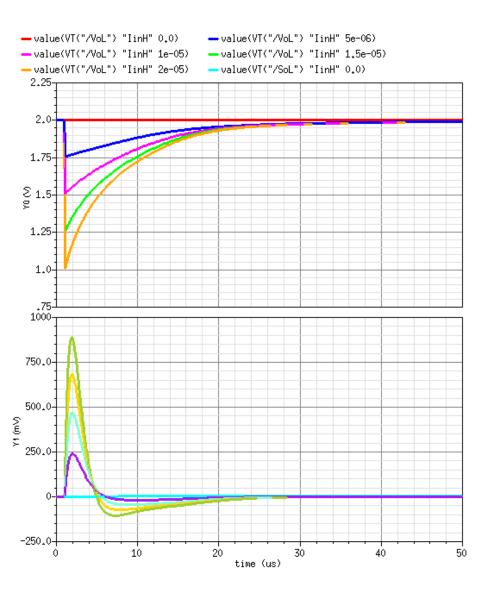

#### Linearity

30M resistor - no capacitance

30M with capacitance

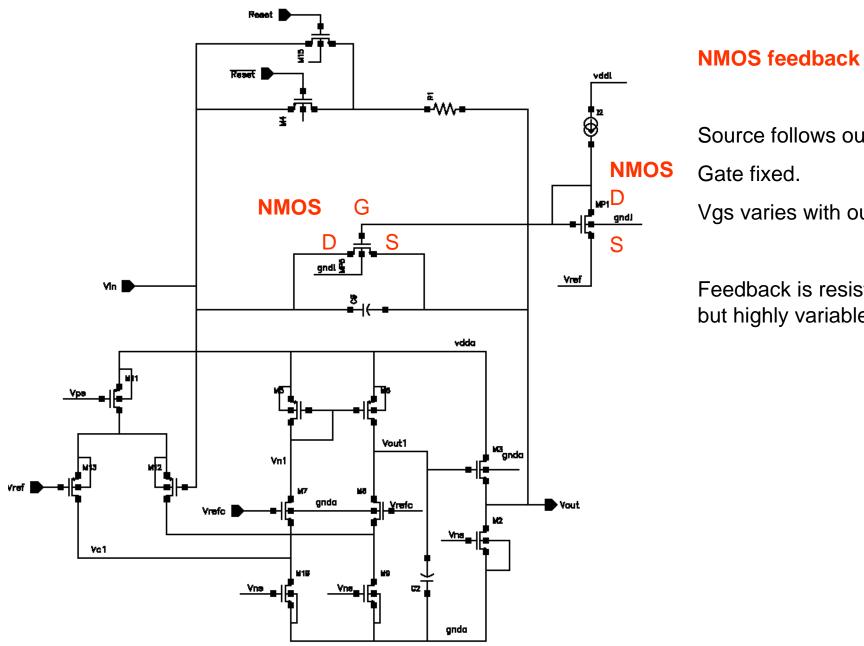

Source follows output

Vgs varies with output

Feedback is resistive, but highly variable

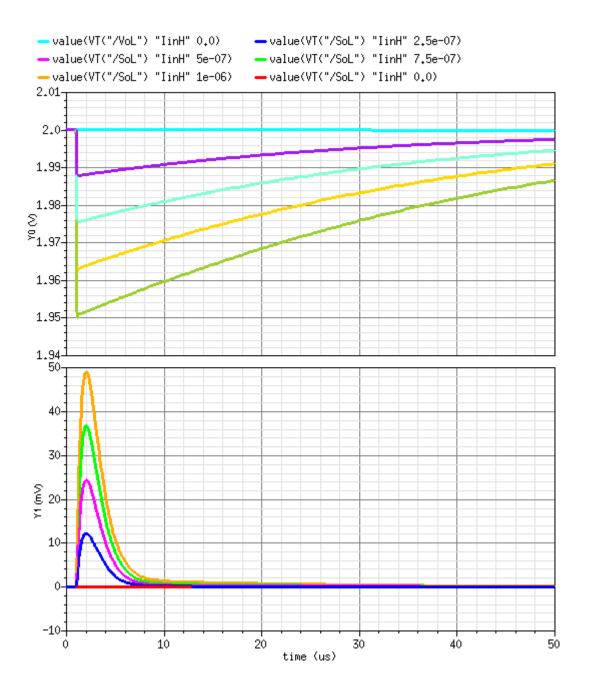

#### W=1um, L=50um feedback device

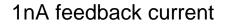

#### Pole-zero adjusted for $30M\Omega$

Undershoot gets worse for large signals

### **NMOS** feedback linearity

1nA feedback current

W=1um, L=50um feedback device

Source at Vref Gate fixed Drain follows output

Vgs constant

Small signals 0-1uA Ifb= 1.3nA W=1um, L=20um

Linear response

Vgs-Vt > Vds

Resistive feedback

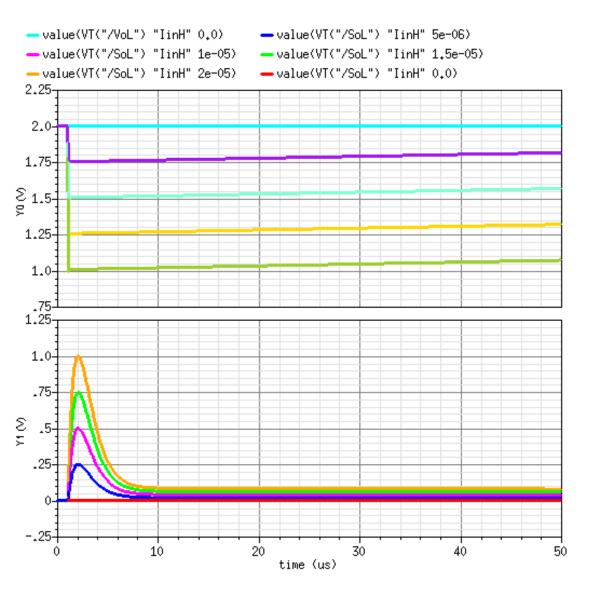

## Large signals 0-20uA

Ifb= 1.3nA

W=1um, L=20um

Saturated response

Vgs-Vt < Vds

Feedback transistor acts as constant current source

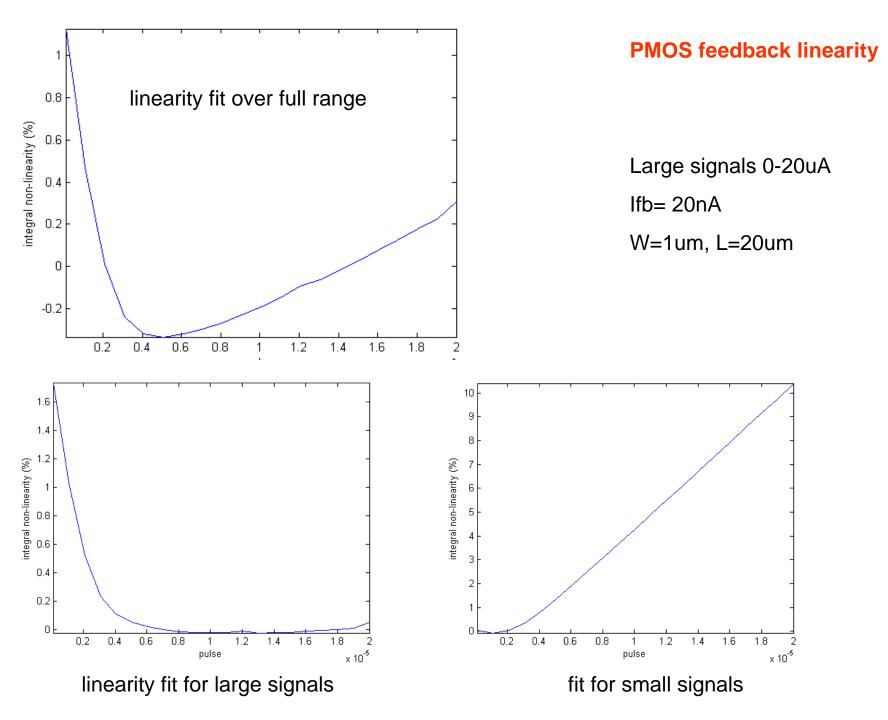

Large signals 0-20uA

Ifb= 20nA

W=1um, L=20um

No pole-zero cancellation,

slow recovery

Large signals 0-20uA Ifb= 1.3nA W=1um, L=20um

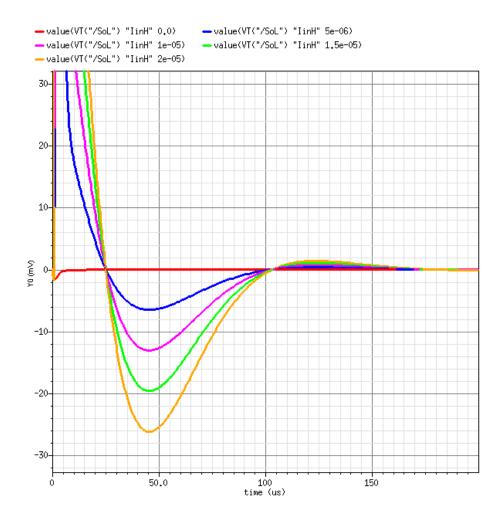

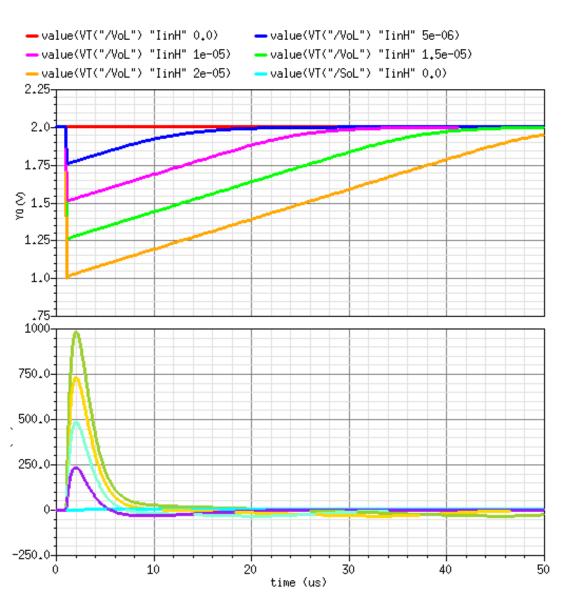

#### **PMOS feedback linearity**

No pole-zero cancellation

Large signals 0-20uA Ifb= 1.3nA W=1um, L=20um

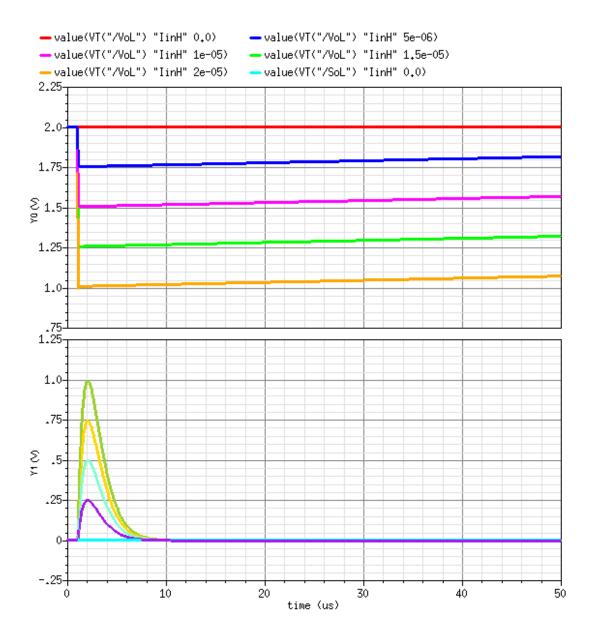

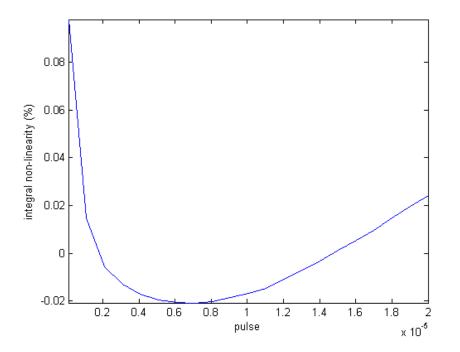

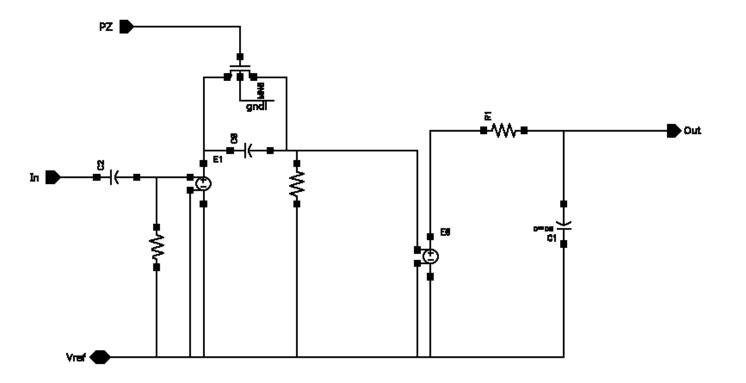

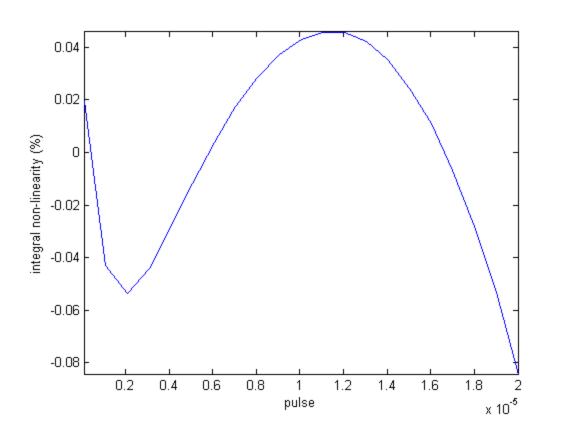

# NMOS linearity compensation

PZ resistor replaced by transistor

Bias conditions match feedback device

# NMOS feedback with compensation

NMOS feedback with compensation

### **Conclusions**

- At least 3 options for amplifier feedback

- 1 resistor linear, but problem with parasitic capacitance

- 2 NMOS variable resistor feedback, difficult to achieve slow preamp recovery

- 3 PMOS current source feedback, linear if recovery is slow.

- Non-linearity can be compensated to some degree

Pole-zero resistor replaced by a transistor at the same bias point as the feedback device